CMOS集成电路设计(二) 接口电路详解

在集成电路(IC)设计中,接口电路扮演着系统内外部或不同模块间“翻译官”与“协调员”的关键角色。随着CMOS工艺成为数字与混合信号芯片的主流技术,其接口电路的设计面临着速度、功耗、噪声与可靠性等多重挑战。本文将深入探讨CMOS集成电路设计中核心接口电路的原理、类型与设计要点。

一、接口电路的重要性与挑战

接口电路位于芯片的边界,负责处理芯片与外部世界(如其他芯片、传感器、存储器件或传输总线)之间的电信号交互。其主要功能包括:

- 电平转换:将芯片内部的核心电压(如1.2V, 0.9V)转换为与外部标准兼容的电压(如3.3V LVCMOS, 1.8V HSTL)。

- 驱动能力增强:提供足够的电流以驱动片外较大的容性负载(如PCB走线、连接器、其他芯片的输入电容)。

- 噪声隔离与抗干扰:抑制外部噪声(如电源噪声、串扰)对内部敏感核心电路的影响,同时减少芯片开关噪声对外部的辐射。

- 速度匹配与同步:在高速传输中,处理信号时序、建立保持时间,并可能集成时钟数据恢复(CDR)或锁相环(PLL)功能。

在纳米级CMOS工艺下,设计挑战尤为突出:核心电压不断降低以节省功耗,但I/O电压可能仍需维持较高水平以兼容旧系统或满足噪声容限要求,这增大了电平转换的设计难度。速度提升导致信号完整性(如反射、振铃、串扰)和功耗(特别是动态功耗)问题愈发严峻。

二、核心接口电路类型详解

1. 输入缓冲器(Input Buffer)

输入缓冲器是外部信号进入芯片的第一道门户。其基本设计要求是:

- 高输入阻抗:最小化对前级驱动电路的负载效应。

- 确定的逻辑阈值:能准确识别高、低电平,通常通过一个反相器链实现。对于不同标准(如TTL, CMOS),阈值需要调整。

- 抗静电放电(ESD)保护:集成ESD保护结构(如GGNMOS、二极管钳位),防止芯片在制造、运输和使用中被静电损坏。

- 施密特触发器输入:对于缓慢变化或伴有噪声的输入信号,采用具有滞回特性的施密特触发器可以提高噪声容限,避免误触发。

2. 输出缓冲器(Output Buffer / Driver)

输出缓冲器负责将内部逻辑信号驱动到片外。其核心是一个按比例放大的反相器链( tapered buffer )。设计要点包括:

- 驱动强度选择:根据负载电容和所需上升/下降时间,计算最终级晶体管的尺寸。驱动能力通常以驱动多大容性负载下的标准上升时间来标定(如50pF @ 5ns)。

- 可控压摆率:通过控制预驱动级的电流或使用串联电阻,限制输出信号的压摆率(slew rate),以减少高速切换时的电源噪声和电磁干扰(EMI)。

- 开漏输出:某些应用(如I²C总线)需要开漏输出,仅提供下拉路径,上拉由外部电阻完成,便于实现“线与”功能。

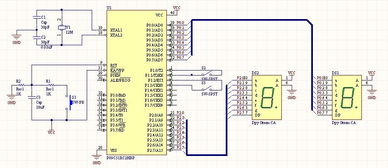

3. 双向输入/输出(Bidirectional I/O)

许多芯片引脚需要复用为输入或输出。这通过三态缓冲器实现:

- 结构:包含一个输出驱动器和一个输入接收器,由一个使能信号控制方向。当使能有效时,引脚作为输出;无效时,输出级处于高阻态,引脚作为输入。

- 关键设计:确保模式切换时无冲突电流(即输出级关闭与输入级开启的时序要配合好),并处理好使能信号路径的延迟,防止“自冲突”。

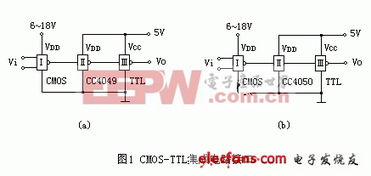

4. 电平转换器(Level Shifter)

这是连接不同电压域的核心电路。常见类型有:

- 低到高电平转换器:将核心低电压信号(如VDDL=1.0V)转换到I/O高电压域(如VDDH=3.3V)。经典结构是交叉耦合的PMOS负载差分对,利用高电压域电源进行锁存,确保输出满摆幅。

- 高到低电平转换器:相对简单,通常一个由高电压域供电、阈值经过设计的反相器即可实现,但需注意栅氧可靠性(避免高电压直接加在薄栅氧晶体管上)。

- 双向电平转换器:用于双向总线,结构更为复杂,需要自动感知信号方向并进行相应转换。

5. 高速接口电路

对于串行接口(如SerDes)、存储器接口(如DDR)等,接口电路更加复杂:

- 差分信号:使用LVDS(低压差分信号)、CML(电流模逻辑)等差分I/O,以提高抗共模噪声能力和速度。

- 阻抗匹配:集成片内终端电阻(如DDR的ODT),并与PCB传输线特性阻抗匹配,减少反射。

- 时序调整:集成可编程延迟线、DLL(延迟锁相环)来精确控制数据与时钟的相位关系。

- 预加重与均衡:在发送端进行预加重(预失真),在接收端进行均衡(如CTLE),以补偿信道的高频损耗,提高数据率。

三、设计考虑与趋势

- 电源与地隔离:I/O电路通常使用独立的电源焊盘和地焊盘(“干净”的I/O VDD/VSS),并与核心电源/地通过片上或封装电感进行隔离,以防止“地弹”和“电源噪声”相互串扰。

- ESD与闩锁效应防护:除了I/O焊盘本身的ESD结构,整个I/O环与核心区域之间需要布置保护环(Guard Ring)以防止闩锁效应。

- 先进封装的影响:随着Chiplet、2.5D/3D集成技术的发展,接口电路需要适应更短距离、更高密度的互连(如硅通孔TSV、微凸块),设计重点转向极低功耗、极高带宽的近距离接口协议。

- 工艺协同优化:先进工艺节点通常提供多种厚栅氧I/O晶体管选项,专门用于承受更高的I/O电压,设计时需要合理选择。

###

接口电路是CMOS集成电路通向物理世界的桥梁,其性能直接影响整个系统的稳定性、速度与兼容性。优秀的设计需要在速度、功耗、面积、鲁棒性之间取得精妙平衡,并深入理解工艺特性、封装模型与系统应用需求。随着系统复杂度和数据速率持续攀升,接口电路的设计将继续是集成电路工程中一个充满挑战与创新的关键领域。

如若转载,请注明出处:http://www.datiantongchen.com/product/72.html

更新时间:2026-04-14 04:51:54