数字集成电路版图设计 附录与持续补充

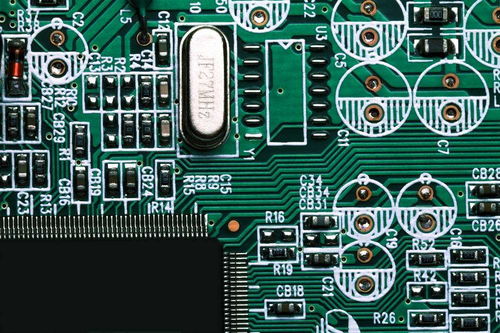

数字集成电路(IC)版图设计是连接电路设计与物理实现的关键环节,它将逻辑网表转化为可在硅片上制造的几何图形。随着工艺节点不断演进,版图设计的复杂性日益增加,附录与持续补充成为学习和实践中的重要部分。

一、附录的核心价值

附录通常包含以下关键内容:

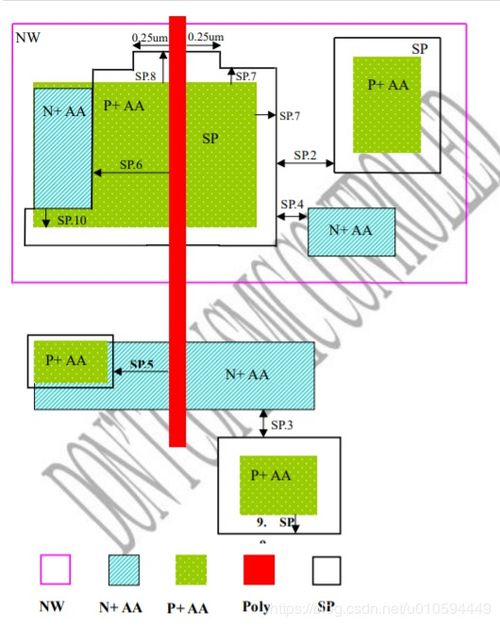

- 工艺设计规则(Design Rules):详细列出制造工艺对版图层、间距、宽度等几何参数的限制,确保设计的可制造性。

- 标准单元库文档:提供标准逻辑单元(如与门、触发器)的版图视图、时序模型和功耗数据,是自动化布局布线的基础。

- 电气规则检查(ERC)与设计规则检查(DRC)指南:解释常见错误类型及解决方法,帮助设计者提前规避物理验证失败的风险。

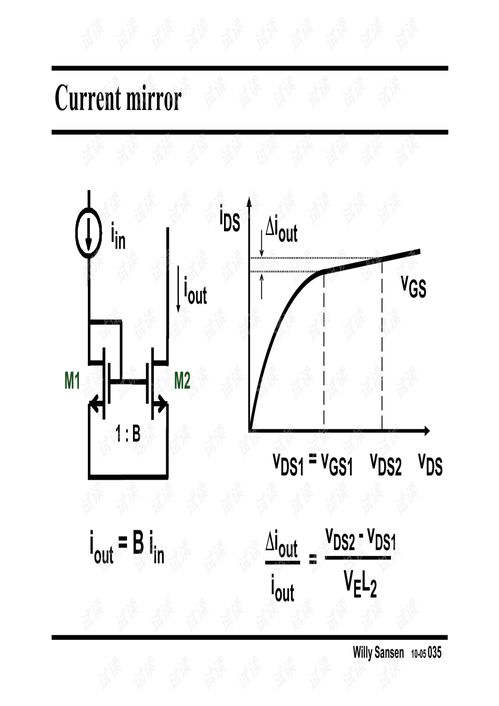

- 版图与电路图对应表:辅助理解晶体管级电路与版图几何形状的映射关系,尤其在定制设计(如模拟模块)中至关重要。

二、持续补充的必要性

由于半导体技术快速迭代,版图设计知识需不断更新:

- 先进工艺挑战:在7纳米及以下节点,量子效应、寄生参数和工艺变异的影响显著,需要补充针对性的版图优化技术(如多图案分解、冗余通孔插入)。

- 工具演进:EDA工具(如Cadence、Synopsys平台)的新功能与脚本使用方法需及时纳入实践指南。

- 新兴设计范式:三维集成电路(3D-IC)、近似计算等新兴领域对版图提出了异构集成、热管理等新要求。

三、集成电路设计全流程中的版图定位

版图设计并非孤立环节,需与前端设计协同:

- 逻辑综合与版图规划:通过物理综合工具预估布线拥塞和时序,提前调整模块布局。

- 功耗完整性分析:补充电源网络设计规则,避免IR压降和电迁移导致的可靠性问题。

- 可制造性设计(DFM):引入基于模型的规则,如化学机械抛光(CMP)补偿图形,提升芯片良率。

四、实践建议

- 建立知识库:将项目经验(如天线效应修复、 latch-up防护)整理为案例库,形成可复用的附录内容。

- 动态更新机制:定期跟踪晶圆厂技术文件更新、学术会议(如ISSCC)成果,迭代补充设计方法。

- 跨领域融合:关注封装技术(如硅通孔TSV)对版图的影响,拓展系统级视角。

###

数字集成电路版图设计是工程与艺术的结合,附录与持续补充既是技术文档,也是设计智慧的沉淀。唯有通过系统化积累与动态演进,才能驾驭纳米尺度下的设计挑战,最终实现高性能、高可靠性的芯片产品。

如若转载,请注明出处:http://www.datiantongchen.com/product/81.html

更新时间:2026-04-16 23:23:40