芯片压缩 集成电路设计中的关键技术解析

在当今高速发展的信息时代,集成电路(IC)设计正面临着日益复杂的挑战。随着电子设备功能不断增强,芯片的尺寸、功耗和性能优化成为设计中的核心议题。其中,芯片压缩技术作为集成电路设计的关键环节,正逐渐受到行业的高度重视。

1. 芯片压缩的概念与意义

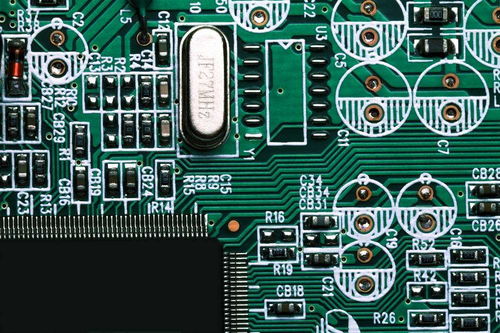

芯片压缩并非指物理尺寸的简单缩小,而是指通过一系列设计优化手段,在保证芯片性能的前提下,减少其逻辑复杂度、功耗和面积。这一技术对于提升芯片的集成度、降低生产成本以及延长设备续航时间具有重要意义。随着摩尔定律的逐步逼近物理极限,芯片压缩技术成为延续半导体行业发展动力的重要途径之一。

2. 集成电路设计中的压缩方法

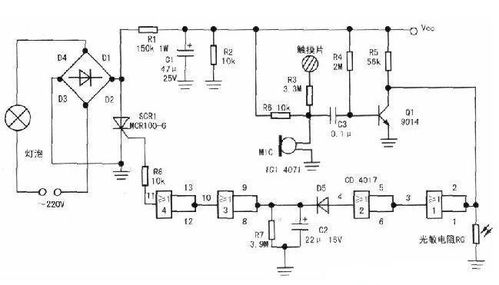

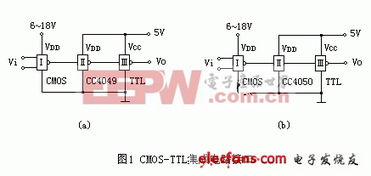

在集成电路设计流程中,芯片压缩主要通过以下几种方式实现:

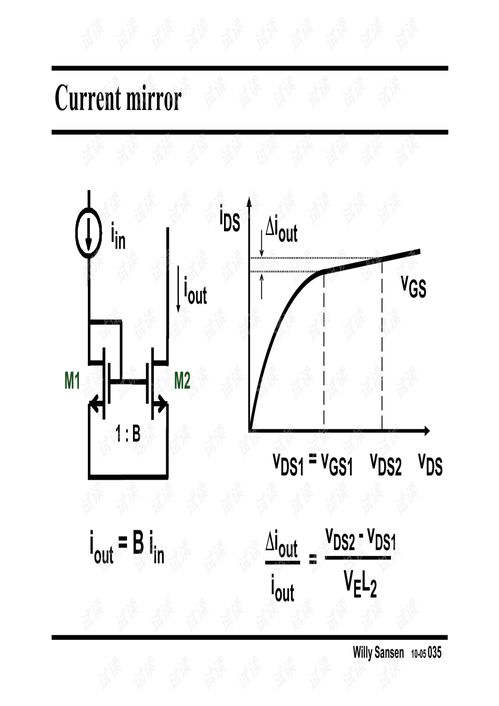

- 逻辑压缩:通过优化布尔逻辑表达式,减少逻辑门的数量,从而降低芯片的复杂度和功耗。

- 物理压缩:在布局与布线阶段,采用先进的算法优化晶体管和连线的排布,以最小化芯片面积。

- 数据压缩:针对存储器模块,应用压缩算法减少数据存储空间,提升存储效率。

- 功耗压缩:通过动态电压频率调整(DVFS)、时钟门控等技术,降低芯片运行时的能耗。

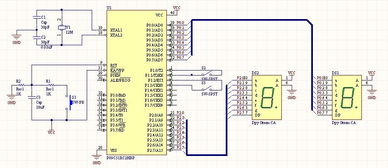

3. 芯片压缩技术的实际应用

芯片压缩技术已广泛应用于各类集成电路设计中。例如,在移动处理器领域,通过逻辑和物理压缩,芯片厂商能够在有限的空间内集成更多功能模块,提升处理能力的同时控制发热和能耗。在人工智能芯片设计中,数据压缩技术帮助优化神经网络模型的存储与计算,大幅提升推理效率。在物联网设备中,低功耗压缩技术使得微型芯片能够长时间运行,推动了智能穿戴、环境监测等场景的发展。

4. 未来发展趋势与挑战

随着5G、人工智能、量子计算等前沿技术的兴起,芯片压缩技术将面临新的机遇与挑战。一方面,新材料(如二维材料)和新架构(如三维集成)的出现为压缩技术提供了更多可能性;另一方面,设计复杂度的增加和物理极限的逼近要求更高效的压缩算法。跨学科合作将成为推动芯片压缩技术创新的关键,结合机器学习、优化理论等多领域知识,实现智能化的设计自动化工具。

芯片压缩技术是集成电路设计中不可或缺的一环。它不仅关乎单个芯片的性能与成本,更影响着整个电子产业的可持续发展。通过不断优化压缩方法,我们有望在有限的物理空间内创造无限的计算可能,为数字化时代的进步奠定坚实基础。

如若转载,请注明出处:http://www.datiantongchen.com/product/65.html

更新时间:2026-04-14 04:09:58