2022年超大规模集成电路可测性设计(DFT)技术与实践培训综述

随着集成电路工艺节点持续微缩,芯片规模与复杂度呈指数级增长,可测性设计已成为确保芯片功能正确、提升良率、控制成本的关键环节。2022年,针对超大规模集成电路的可测性设计技术与实践培训,紧密围绕产业前沿需求,系统性地探讨了DFT的核心原理、关键技术及工程实现。

一、培训核心内容聚焦

本次培训深入剖析了超大规模集成电路面临的测试挑战,如测试数据量爆炸、测试功耗控制、测试时间压缩等。核心教学内容覆盖了三大DFT主流技术:

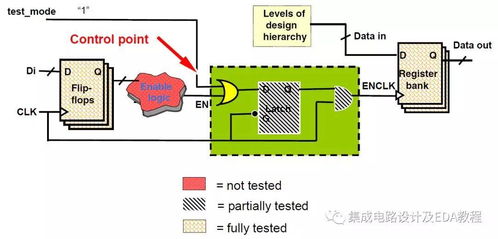

1. 扫描设计:详细讲解了全扫描与部分扫描设计方法,包括扫描链插入、时钟控制、测试向量生成与压缩技术,重点探讨了如何平衡面积开销与测试覆盖率。

2. 内建自测试:系统介绍了存储器BIST和逻辑BIST的架构设计、算法实现及结果分析,强调了在SoC中嵌入BIST模块以实现高效自检的策略。

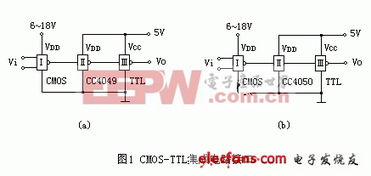

3. 边界扫描:依据IEEE 1149.1等标准,阐述了边界扫描在板级与芯片级互联测试、内核测试中的应用,并探讨了其在系统级调试中的作用。

培训还涉及了基于ATPG的故障模型、测试功耗管理、可测试性设计规则检查等高级议题。

二、实践与工具环节

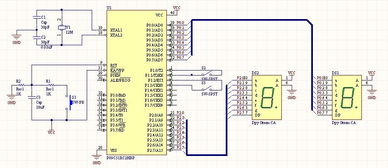

理论与实践相结合是本次培训的亮点。通过主流EDA工具(如Synopsys、Cadence、Siemens EDA的相关DFT工具链)的上机操作,学员亲身体验了从RTL设计插入DFT结构,到生成测试向量并进行故障仿真的完整流程。实践案例聚焦于当前热门的先进工艺节点芯片和复杂SoC,使学员能够直面高速接口测试、低功耗设计测试等实际工程难题。

三、行业趋势与展望

培训结合2022年技术动态,展望了DFT的未来发展方向:

- 与AI/ML融合:利用机器学习优化测试向量生成、故障诊断和良率分析。

- 面向3D-IC与Chiplet:探讨了堆叠芯片和异构集成中新的可测试性挑战与解决方案,如跨die测试访问。

- 全生命周期测试:强调DFT技术需支持芯片从生产测试到系统现场运行的健康监控与预测性维护。

2022年的DFT技术与实践培训,不仅夯实了学员在可测性设计领域的基础理论,更通过前沿案例与工具实践,提升了解决超大规模集成电路测试工程问题的综合能力,为助力我国集成电路产业攻克高端芯片测试壁垒提供了重要的人才与技术支撑。

如若转载,请注明出处:http://www.datiantongchen.com/product/67.html

更新时间:2026-04-14 05:21:43