量子计算的理论发展与集成电路设计

量子计算作为一项颠覆性的信息技术,其理论发展与硬件实现正以前所未有的速度推进。理论探索为量子计算奠定了坚实的数学和物理基础,而集成电路设计则是将理论转化为实用化量子处理器的关键桥梁。

量子计算的理论基石

量子计算的理论发展可以追溯到上世纪八十年代。1981年,物理学家理查德·费曼首次提出利用量子系统模拟自然界的构想。大卫·多伊奇于1985年严格定义了量子图灵机,奠定了量子计算的理论框架。核心理论突破包括:

1. 量子比特:超越经典比特的0或1状态,量子比特可以处于叠加态,即同时是0和1的线性组合。

2. 量子纠缠:多个量子比特之间可以形成一种强关联,使得对其中一个的操作会瞬间影响另一个,无论距离多远。这是量子并行性的重要来源。

3. 量子门与算法:一系列量子逻辑门构成了量子电路。肖尔算法(1994年)和格罗弗算法(1996年)的提出,分别展示了量子计算在因数分解和无序数据库搜索上的指数级加速潜力,极大地激发了研究热情。

这些理论进展证明了量子计算机在解决特定问题上具有超越经典计算机的极限能力。

从理论到硬件:集成电路设计的挑战

将精妙的量子理论转化为物理现实是巨大的挑战。现代量子处理器(QPU)的核心,正是借鉴并超越了经典集成电路设计的理念。

- 量子比特的实现:目前主流的物理实现方案,如超导电路、离子阱、半导体量子点等,本质上都需要精密的“芯片”级设计。例如,超导量子比特需要在极低温下,于硅或蓝宝石衬底上制备出微米或纳米尺度的约瑟夫森结和电容、电感结构,构成可操控的量子谐振电路。这本身就是一种特殊的集成电路。

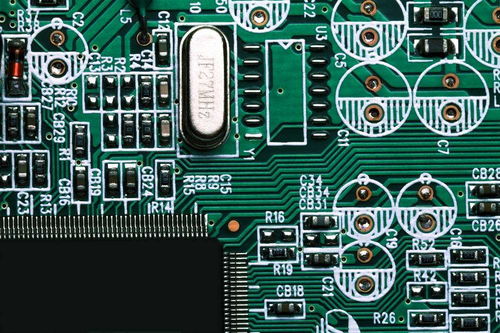

- 可扩展性与集成:理论要求量子计算机需要成千上万个乃至百万个逻辑量子比特(通过量子纠错获得)才能实现实用优势。这就要求量子芯片必须像经典CPU一样,具备高度集成和可扩展的能力。设计重点包括:

- 比特密度:在有限的芯片面积内集成更多物理量子比特,并尽量减少串扰。

- 互连与布线:设计高效的量子比特间耦合(用于实现两比特量子门)以及控制信号、读取信号的经典导线网络,同时要避免引入噪声和热量。

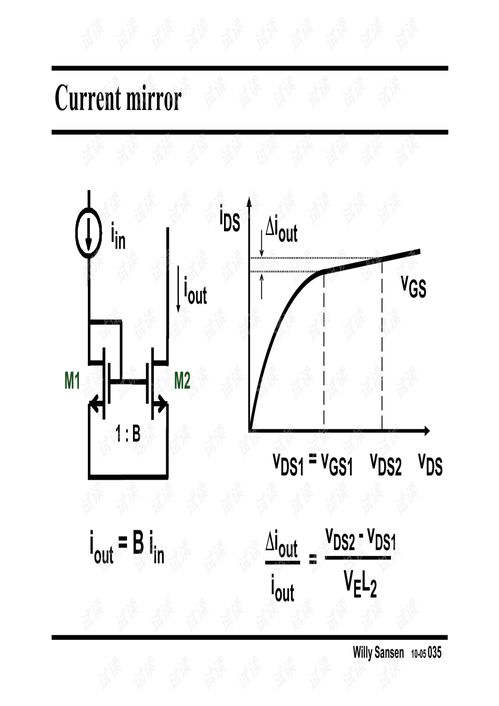

- 控制与读取电路:需要将精密的微波脉冲、电压脉冲等控制信号,以及极微弱的量子态读取信号,与室温下的经典电子控制系统无缝集成。这催生了“低温CMOS”等混合集成电路技术。

- 噪声、纠错与架构协同:量子态极其脆弱,易受环境噪声干扰。理论上的量子纠错码(如表面码)要求特定的物理比特连接拓扑结构(如二维网格)。集成电路设计必须与纠错理论紧密结合,在物理布局上实现所需的连接性,并优化设计以最大限度地降低原生错误率。

展望:理论引导下的设计革命

量子计算的理论发展与集成电路设计是相辅相成的。新的量子算法和纠错方案不断对硬件提出新的要求;反过来,硬件实现的进展(如比特数量的增长、保真度的提升)也为验证更复杂的理论模型和算法提供了实验平台。

量子计算的发展将更加依赖于理论物理学家、计算机科学家与微电子工程师的深度协作。面向容错量子计算的专用集成电路设计,将成为继经典CPU、GPU之后,微电子领域又一个技术制高点,最终推动量子计算从实验室走向实际应用。

如若转载,请注明出处:http://www.datiantongchen.com/product/71.html

更新时间:2026-04-14 19:26:51